ENTWICKLUNGSPROZESSE I WERKZEUGE I PLATTFORMEN

FÜR SICHERHEITSKRITISCHE MULTICORESYSTEME

### Multicore-Plattformen und Architekturpattern

GEFÖRDERT VOM

### Agenda

# Überblick & Einleitung

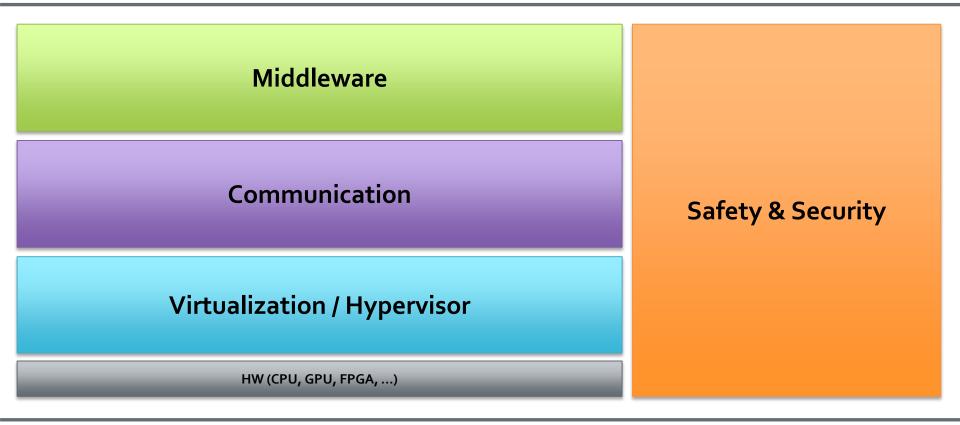

Virtualisierung / Hypervisor

Safety & Security

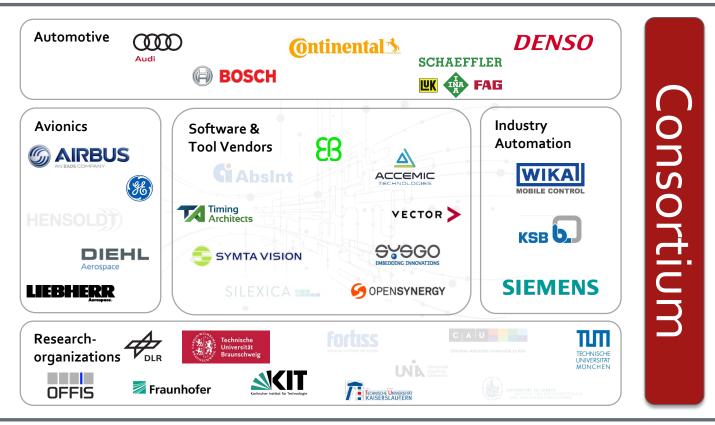

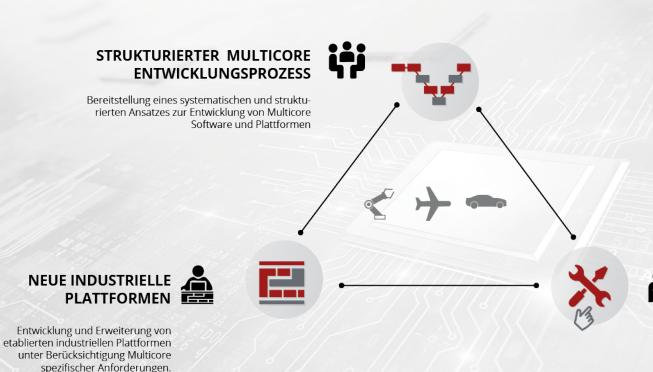

### TP4 Industrielle Plattformen für Multicore Systeme

Industrieautomatisierung

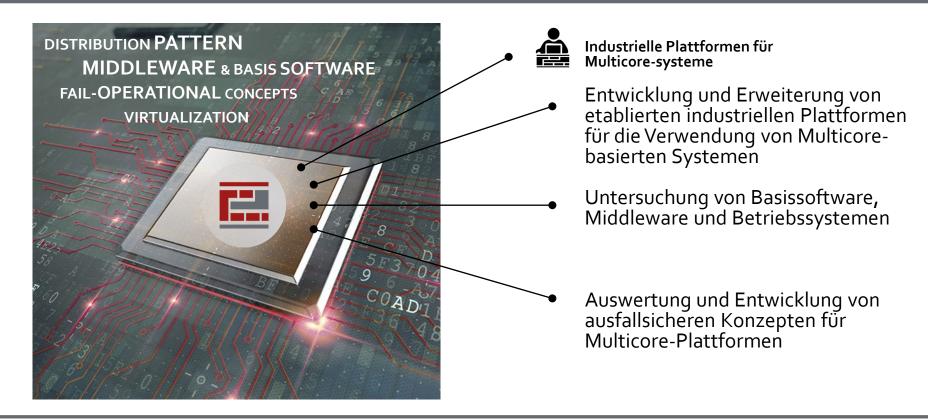

### TP4 Industrielle Plattformen für Multicore Systeme

### TP4 Industrielle Plattformen für Multicore Systeme

Plattform Architekturen und Distributionsmuster

MIDDLEWARE HIERARCHICAL SCHEDULING

VIRTUALIZATION & HYPERVISORS

COMMUNICATION

**CODE QUALITY**

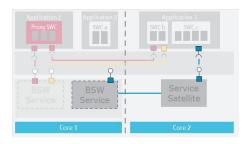

**BSW DISTRIBUTION**

Synchronisation und Kommunikation

RESOURCE BROKERING

MIXED CRITICALITY QUALITY-OF-SERVICE

TIME DIVISION MULTIPLEXING REAL-TIME

RELIABILITY NETWORK ON CHIP

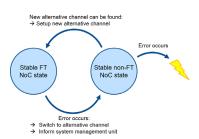

Evaluierung und Entwicklung von failoperational Konzepten FAILURE MODES SWITCHOVER MECHANISMS

ISO 26262 FAILURE DIAGNOSIS

SIMPLEX ARCHITECTURE

FAULT TOLERANCE REDUNDANCY

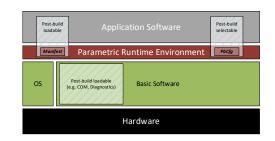

#### Middleware

- Parametrisierbare

Laufzeitumgebung für ECUs

- Master-Satelliten-Muster in AUTOSAR

- Hierarchisches Scheduling für Steuereinheiten

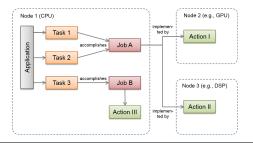

- Aufgabenmanagement in heterogenen Systemen

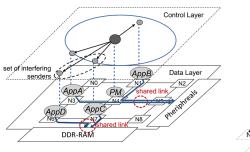

#### Kommunikation

- Niedrige Latenzzeiten und Echtzeit

- Kommunikationsschicht f

ür On-Chip Netzwerke

- Kommunikationssemantik und Modelltransformation

- Interprozessorkommunikation in heterogenen Architekturen

## ENTWICKLUNGSPROZESSE I WERKZEUGE I PLATTFORMEN FÜR SICHERHEITSKRITISCHE MULTICORESYSTEME

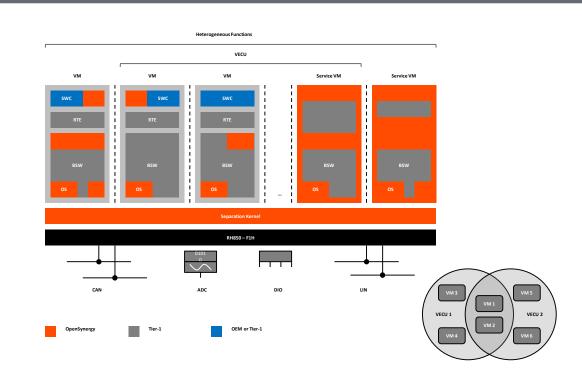

#### Virtualisierung / Hypervisor

- Virtualisierung heterogener Systeme

- Online-Überwachung des Hypervisor-Betriebs

- Virtualisierung in ressourcenbeschränkten Geräten

- Modellbasierte Beschreibung der Hypervisor-Einstellungen und Codegenerierung

- Embedded hypervisor

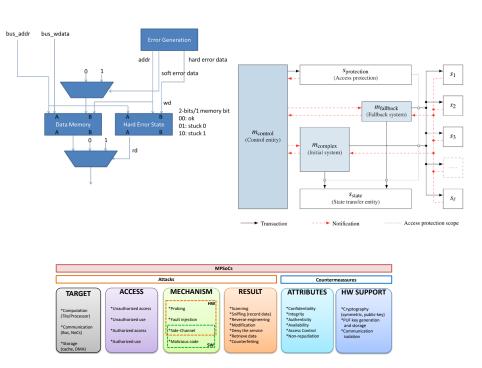

#### Safety & Security

- Sicherstellung und Vertragsgestaltung

- Hypervisor-Codequalität

- Bedrohungsmodelle und Risikominimierung

- Dynamische Migration von kritischen Funktionen für heterogene SoCs

- Ausfallsichere "switch-over" Mechanismen

- Effizienter, ausfallsicherer Multicore-Prozessor

- Sichere (secure) Schnittstelle zu Modulen außerhalb eines Chips

- Analyse ausfallsicherer Konzepte auf der System-Ebene

- Sicherheit (safety) Isolierte Kanäle

- Absicherung von OS-Kernels

### Zusammenfassung & Ausblick

Entwicklung von Methoden und Werkzeugen, welche den strukturierten Multicore Entwicklungsprozess unterstützen

### Zusammenfassung und Ausblick